2020年10月3日

Zephyr OSで遊ぼう その16 - SMP対応の準備、コンテキストスイッチの実装、後編1、RISC-Vのコンテキストスイッチ

目次: Zephyr

前回は、AArch64の実装を調べました。いよいよ新しい方式のコンテキストスイッチを実装したいところですが、その前にもう一つだけRISC-Vの既存実装を調べます。

RISC-Vの2つのコンテキストスイッチ経路

RISC-V向け実装において、コンテキストスイッチが行われる条件は2つあります。1つはスリープしたときなどに呼ばれる明示的なコンテキストスイッチです。do_swap() を経由します。もう1つは割り込み発生時に行われるプリエンプションです。

- 明示的コンテキストスイッチ

- do_swap() -> arch_switch() ラッパー関数 -> z_riscv_switch() -> ecall -> __irq_wrapper -> is_syscall -> reschedule -> no_reschedule -> mret

- プリエンプション

- (任意の場所) -> __irq_wrapper -> is_interrupt -> on_irq_stack -> 割り込みハンドラ(isr_timer() など) -> on_thread_stack -> reschedule -> no_reschedule -> mret

明示的コンテキストスイッチについては、以前(2020年9月29日の日記参照)実装したラッパー関数がスタート地点となります。コードを変更する前に、従来のコンテキストスイッチがどんな経路を通るか確認します。

arch_switch() ラッパー関数 -> z_riscv_switch() -> ecall -> __irq_wrapper -> is_syscall

// zephyr/arch/riscv/include/kernel_arch_func.h

static inline void arch_switch(void *switch_to, void **switched_from)

{

z_riscv_switch(switch_to, switched_from);

}

// zephyr/arch/riscv/core/swap.S

/*

* void z_riscv_switch(void *switch_to, void **switched_from)

*/

SECTION_FUNC(exception.other, z_riscv_switch)

/* Make a system call to perform context switch */

ecall //★例外を発生させる★

jalr x0, ra

// zephyr/arch/riscv/core/isr.S

/*

* Handler called upon each exception/interrupt/fault

* In this architecture, system call (ECALL) is used to perform context

* switching or IRQ offloading (when enabled).

*/

SECTION_FUNC(exception.entry, __irq_wrapper)

/* Allocate space on thread stack to save registers */

addi sp, sp, -__z_arch_esf_t_SIZEOF

...

/*

* Check if exception is the result of an interrupt or not.

* (SOC dependent). Following the RISC-V architecture spec, the MSB

* of the mcause register is used to indicate whether an exception

* is the result of an interrupt or an exception/fault. But for some

* SOCs (like pulpino or riscv-qemu), the MSB is never set to indicate

* interrupt. Hence, check for interrupt/exception via the __soc_is_irq

* function (that needs to be implemented by each SOC). The result is

* returned via register a0 (1: interrupt, 0 exception)

*/

jal ra, __soc_is_irq

/* If a0 != 0, jump to is_interrupt */

addi t1, x0, 0

bnez a0, is_interrupt //★割り込みの場合はこちらにジャンプする★

/*

* If the exception is the result of an ECALL, check whether to

* perform a context-switch or an IRQ offload. Otherwise call _Fault

* to report the exception.

*/

csrr t0, mcause

li t2, SOC_MCAUSE_EXP_MASK

and t0, t0, t2

li t1, SOC_MCAUSE_ECALL_EXP

/*

* If mcause == SOC_MCAUSE_ECALL_EXP, handle system call,

* otherwise handle fault

*/

beq t0, t1, is_syscall //★ecallの場合はこちらにジャンプする★

/*

* Call _Fault to handle exception.

* Stack pointer is pointing to a z_arch_esf_t structure, pass it

* to _Fault (via register a0).

* If _Fault shall return, set return address to no_reschedule

* to restore stack.

*/

addi a0, sp, 0

la ra, no_reschedule

tail _Fault //★いずれでもなければ停止させる★

...

Zephyr RISC-V向け実装では、割り込み・例外ハンドラは1つだけです。割り込みも例外も全て __irq_wrapperに飛んできますから、最初の方で要因をチェックして仕分けしています。RISC-Vの規格としては割り込み要因ごとに別の割り込みハンドラに飛べる形式(ベクタ形式)もありますが、Zephyrは使っていません。

明示的コンテキストスイッチの実行経路: is_syscall -> reschedule -> no_reschedule -> mret

// zephyr/arch/riscv/core/isr.S

is_syscall:

/*

* A syscall is the result of an ecall instruction, in which case the

* MEPC will contain the address of the ecall instruction.

* Increment saved MEPC by 4 to prevent triggering the same ecall

* again upon exiting the ISR.

*

* It's safe to always increment by 4, even with compressed

* instructions, because the ecall instruction is always 4 bytes.

*/

RV_OP_LOADREG t0, __z_arch_esf_t_mepc_OFFSET(sp)

addi t0, t0, 4

RV_OP_STOREREG t0, __z_arch_esf_t_mepc_OFFSET(sp)

...

/*

* Go to reschedule to handle context-switch

*/

j reschedule //★コンテキストスイッチ★

...

reschedule:

...

/* Get reference to _kernel */

la t0, _kernel

/* Get pointer to _kernel.current */

RV_OP_LOADREG t1, _kernel_offset_to_current(t0)

/*

* Save callee-saved registers of current thread

* prior to handle context-switching

*/

RV_OP_STOREREG s0, _thread_offset_to_s0(t1)

RV_OP_STOREREG s1, _thread_offset_to_s1(t1)

...

RV_OP_STOREREG s10, _thread_offset_to_s10(t1)

RV_OP_STOREREG s11, _thread_offset_to_s11(t1)

...

/*

* Save stack pointer of current thread and set the default return value

* of z_swap to _k_neg_eagain for the thread.

*/

RV_OP_STOREREG sp, _thread_offset_to_sp(t1)

la t2, _k_neg_eagain

lw t3, 0x00(t2)

sw t3, _thread_offset_to_swap_return_value(t1)

/* Get next thread to schedule. */

RV_OP_LOADREG t1, _kernel_offset_to_ready_q_cache(t0)

/*

* Set _kernel.current to new thread loaded in t1

*/

RV_OP_STOREREG t1, _kernel_offset_to_current(t0)

/* Switch to new thread stack */

RV_OP_LOADREG sp, _thread_offset_to_sp(t1)

/* Restore callee-saved registers of new thread */

RV_OP_LOADREG s0, _thread_offset_to_s0(t1)

RV_OP_LOADREG s1, _thread_offset_to_s1(t1)

...

RV_OP_LOADREG s10, _thread_offset_to_s10(t1)

RV_OP_LOADREG s11, _thread_offset_to_s11(t1)

...

no_reschedule:

...

/* Restore MEPC register */

RV_OP_LOADREG t0, __z_arch_esf_t_mepc_OFFSET(sp)

csrw mepc, t0

/* Restore SOC-specific MSTATUS register */

RV_OP_LOADREG t0, __z_arch_esf_t_mstatus_OFFSET(sp)

csrw mstatus, t0

...

/* Restore caller-saved registers from thread stack */

RV_OP_LOADREG ra, __z_arch_esf_t_ra_OFFSET(sp)

RV_OP_LOADREG gp, __z_arch_esf_t_gp_OFFSET(sp)

RV_OP_LOADREG tp, __z_arch_esf_t_tp_OFFSET(sp)

RV_OP_LOADREG t0, __z_arch_esf_t_t0_OFFSET(sp)

...

RV_OP_LOADREG a6, __z_arch_esf_t_a6_OFFSET(sp)

RV_OP_LOADREG a7, __z_arch_esf_t_a7_OFFSET(sp)

/* Release stack space */

addi sp, sp, __z_arch_esf_t_SIZEOF

/* Call SOC_ERET to exit ISR */

SOC_ERET

コメントが丁寧に書いてあって素晴らしいですね。コンテキストスイッチの手順はAArch64の実装とほぼ同じですが、AAarch64は明示的なコンテキストスイッチとプリエンプションが独立して実装されており、RISC-Vはrescheduleで両者が合流する点が違います。コンテキストスイッチの説明は先日(2020年10月1日の日記参照)の紙芝居が参考になるかと思います。

明示的なコンテキストスイッチとプリエンプションの部分が大体仕分けできました。いよいよ実装に挑みます。続きはまた。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月1日

Zephyr OSで遊ぼう その15 - SMP対応の準備、コンテキストスイッチの実装、中編2、既存実装調査

目次: Zephyr

前回は、新しいコンテキストスイッチ関数に対応しているAArch64の実装のうち、共通部分からアーキテクチャ依存部分に至るまでを調べました。引き続きアーキテクチャ依存部分を調べます。

アーキ依存部分の処理(AArch64)

コンテキストスイッチのアーキテクチャ依存部分(AArch64向けarch_switch())の実装はほぼ全てアセンブラで実装されています。

コンテキストスイッチの本体はz_arm64_context_switchです。x0がnew_thread, x1がold_threadだと思って動きます。コンテキストスイッチの仕事はレジスタの値を切り替え前のスレッド構造体(old_thread)に退避し、切り替え後のスレッド構造体(new_thread)からレジスタの値を復旧させることです。

AArch64の新しい形式のコンテキストスイッチarch_switch() 実装

// zephyr/arch/arm/core/aarch64/switch.S

GTEXT(z_arm64_svc)

SECTION_FUNC(TEXT, z_arm64_svc)

z_arm64_enter_exc x2, x3, x4 /* ★レジスタをスタックに退避(切り替え前のスレッド)★ */

switch_el x1, 3f, 2f, 1f

3:

mrs x0, esr_el3

b 0f

2:

mrs x0, esr_el2

b 0f

1:

mrs x0, esr_el1

0:

lsr x1, x0, #26

cmp x1, #0x15 /* 0x15 = SVC */

bne inv

/* Demux the SVC call */

and x1, x0, #0xff

cmp x1, #_SVC_CALL_CONTEXT_SWITCH

beq context_switch /* ★以下参照★ */

...

context_switch:

/*

* Retrieve x0 and x1 from the stack:

* - x0 = new_thread->switch_handle = switch_to thread

* - x1 = x1 = &old_thread->switch_handle = current thread

*/

ldp x0, x1, [sp, #(16 * 10)] /* ★x1 = 切り替え前、x0 = 切り替え後のスレッド★ */

/* Get old thread from x1 */

sub x1, x1, ___thread_t_switch_handle_OFFSET

/* Switch thread */

bl z_arm64_context_switch /* ★コンテキストスイッチ本体(スタックが切り替わる)★ */

exit:

z_arm64_exit_exc x0, x1, x2 /* ★レジスタをスタックから復旧(切り替え後のスレッド)★ */

...

/**

* @brief Routine to handle context switches

*

* This function is directly called either by _isr_wrapper() in case of

* preemption, or z_arm64_svc() in case of cooperative switching.

*/

GTEXT(z_arm64_context_switch)

SECTION_FUNC(TEXT, z_arm64_context_switch)

/* addr of callee-saved regs in thread in x2 */

ldr x2, =_thread_offset_to_callee_saved

add x2, x2, x1

/* Store rest of process context including x30 */

stp x19, x20, [x2], #16

stp x21, x22, [x2], #16

stp x23, x24, [x2], #16

stp x25, x26, [x2], #16

stp x27, x28, [x2], #16

stp x29, x30, [x2], #16

/* Save the current SP */

mov x1, sp

str x1, [x2]

/* addr of callee-saved regs in thread in x2 */

ldr x2, =_thread_offset_to_callee_saved

add x2, x2, x0

/* Restore x19-x29 plus x30 */

ldp x19, x20, [x2], #16

ldp x21, x22, [x2], #16

ldp x23, x24, [x2], #16

ldp x25, x26, [x2], #16

ldp x27, x28, [x2], #16

ldp x29, x30, [x2], #16

ldr x1, [x2]

mov sp, x1 /* ★ここで切り替え後のスレッドのスタックに変わる★ */

#ifdef CONFIG_TRACING

stp xzr, x30, [sp, #-16]!

bl sys_trace_thread_switched_in

ldp xzr, x30, [sp], #16

#endif

/* We restored x30 from the process stack. There are three possible

* cases:

*

* - We return to z_arm64_svc() when swapping in a thread that was

* swapped out by z_arm64_svc() before jumping into

* z_arm64_exit_exc()

* - We return to _isr_wrapper() when swapping in a thread that was

* swapped out by _isr_wrapper() before jumping into

* z_arm64_exit_exc()

* - We return (jump) into z_thread_entry_wrapper() for new threads

* (see thread.c)

*/

ret

// zephyr/include/arm/aarch64/thread.h

struct _callee_saved {

uint64_t x19;

uint64_t x20;

uint64_t x21;

uint64_t x22;

uint64_t x23;

uint64_t x24;

uint64_t x25;

uint64_t x26;

uint64_t x27;

uint64_t x28;

uint64_t x29; /* FP */

uint64_t x30; /* LR */

uint64_t sp;

};

コードを見て一発で理解するのは厳しいので、処理の概要を書いておきます。

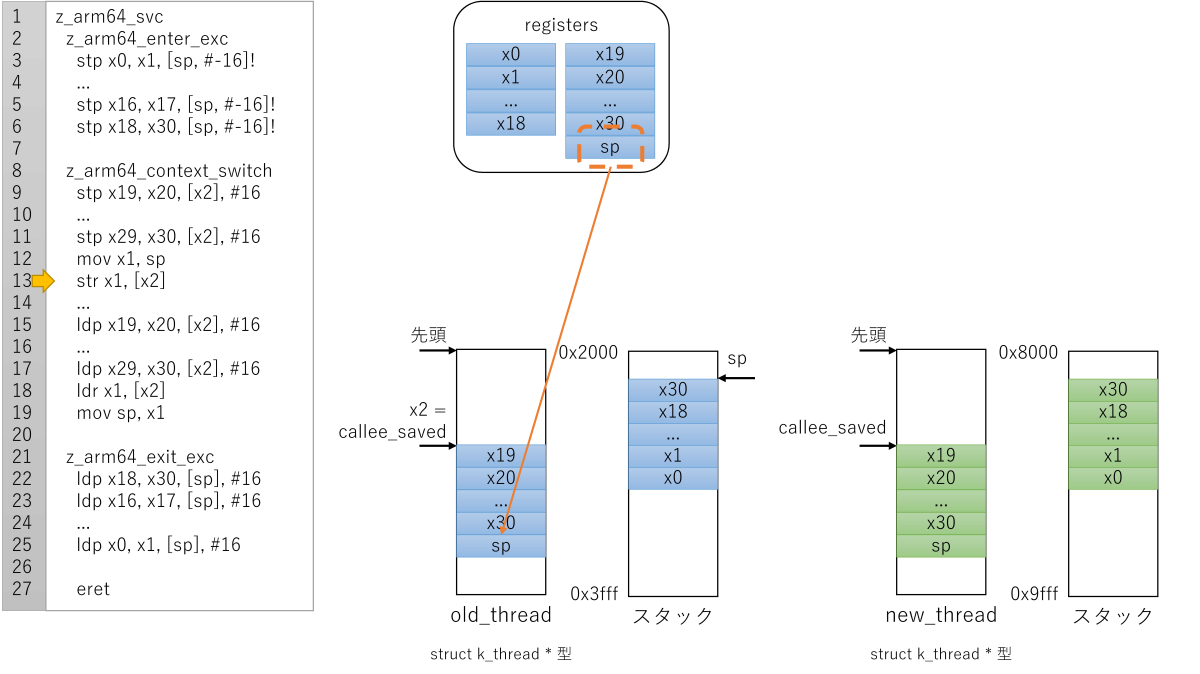

コンテキストスイッチの際にスタックが切り替わります。z_arm64_exit_exc x0, x1, x2はシステムコールを呼んだスレッド(=切り替え前のスレッド)ではなく、コンテキストスイッチ後のスレッドのスタックからレジスタを復旧します。

これも文章だと何だかわからないので、紙芝居を書いておきます。

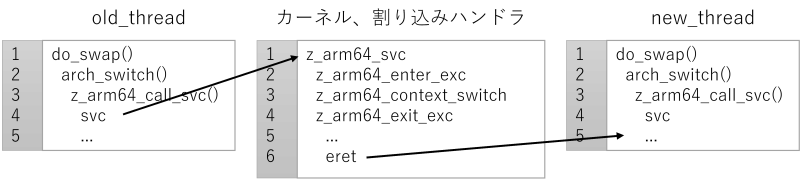

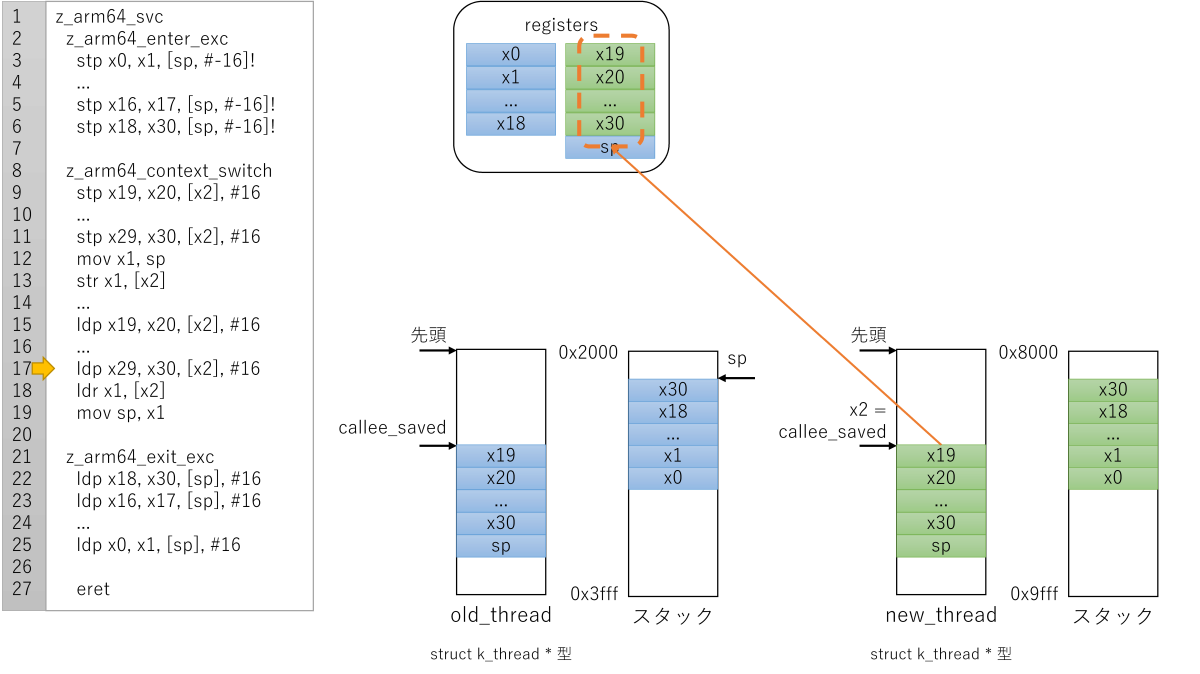

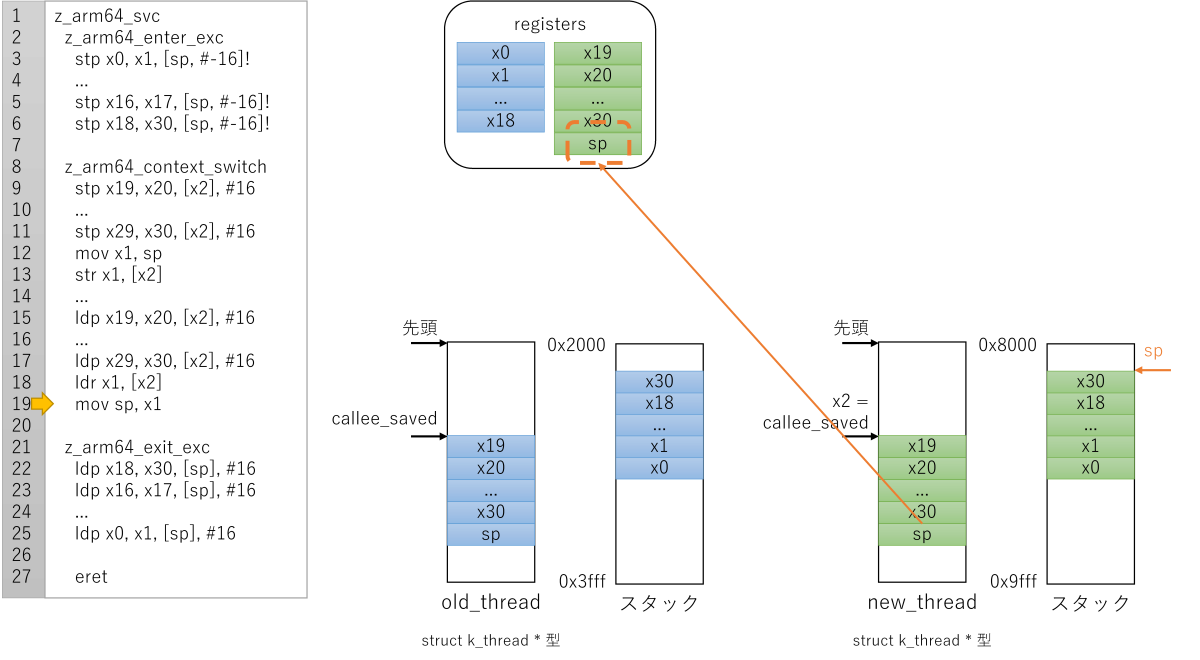

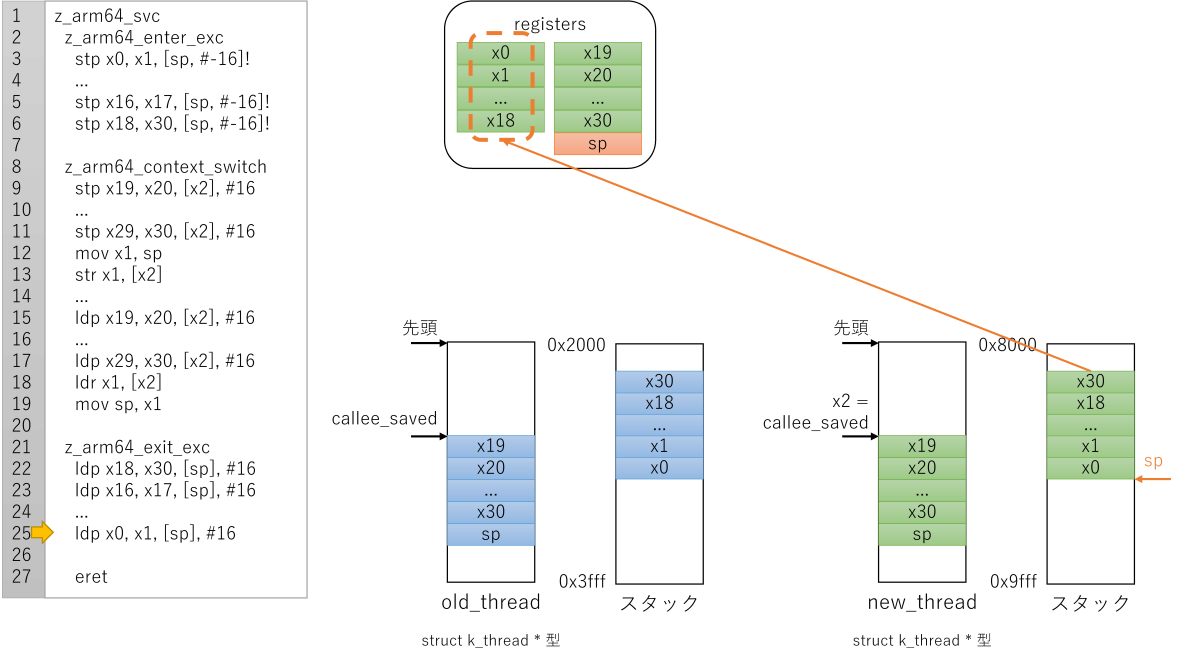

Zephyr AArch64のコンテキストスイッチ: 例外ハンドラ先頭

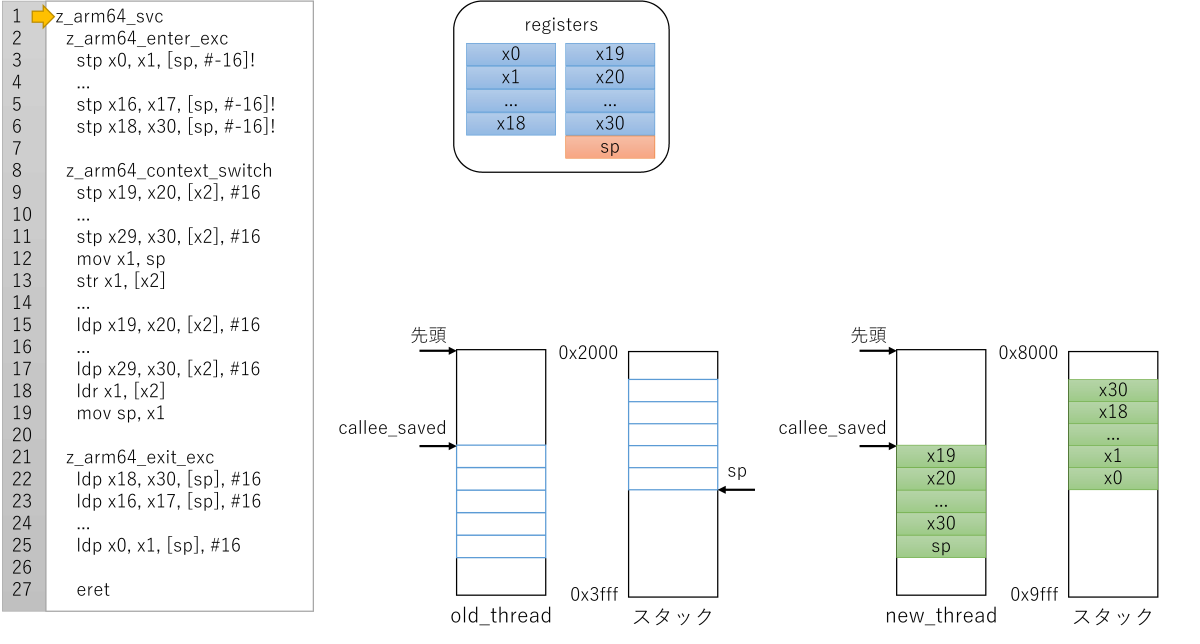

Zephyr AArch64のコンテキストスイッチ: 例外ハンドラ入り口、スタックへレジスタ退避

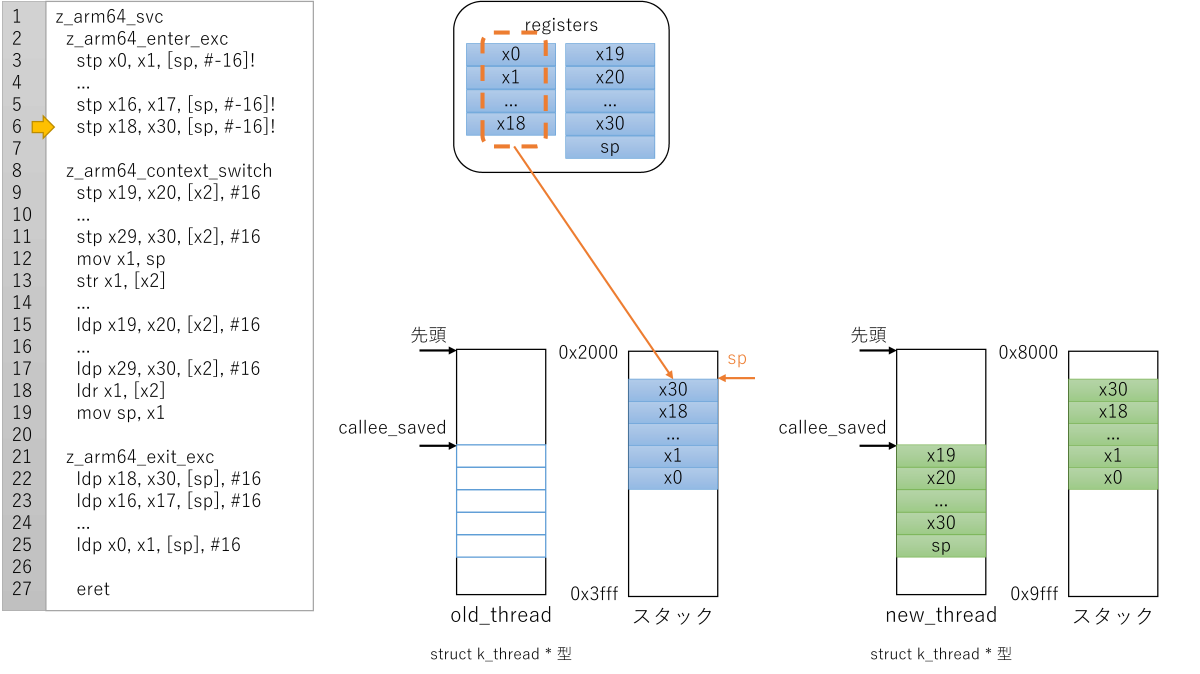

Zephyr AArch64のコンテキストスイッチ: コンテキストスイッチ前半、切り替え前スレッド構造体へレジスタ退避

Zephyr AArch64のコンテキストスイッチ: コンテキストスイッチ前半、切り替え前スレッド構造体へスタックポインタ退避

Zephyr AArch64のコンテキストスイッチ: コンテキストスイッチ後半、切り替え後スレッド構造体からレジスタ復旧

Zephyr AArch64のコンテキストスイッチ: コンテキストスイッチ後半、切り替え後スレッド構造体からスタックポインタ復旧(=スタック切り替え)

Zephyr AArch64のコンテキストスイッチ: 例外ハンドラ入り口、切り替え後のスタックからレジスタ復旧

図には書きませんでしたが、例外からリターンする命令(eret命令)が参照するレジスタ(SPSR, ELRレジスタ)もスタックに退避、復旧しています。従ってeretが戻る先は切り替え後のスレッドのコードです。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年9月30日

Zephyr OSで遊ぼう その14 - SMP対応の準備、コンテキストスイッチの実装、中編1、既存実装調査

目次: Zephyr

前回は、新しい形式のコンテキストスイッチ関数arch_switch() のラッパー関数まで実装しました。RISC-V向け実装をする前に、既に新しいコンテキストスイッチ関数に対応しているAArch64の実装を調べます。

共通部分からアーキ依存部分

コンテキストスイッチ処理の共通部分(do_swap())から、アーキテクチャ依存部分(AArch64のarch_switch())に至るまでを見ます。

Zephyrの新しい形式のコンテキストスイッチ関数(共通部分)

// zephyr/kernel/include/kswap.h

/* New style context switching. arch_switch() is a lower level

* primitive that doesn't know about the scheduler or return value.

* Needed for SMP, where the scheduler requires spinlocking that we

* don't want to have to do in per-architecture assembly.

*

* Note that is_spinlock is a compile-time construct which will be

* optimized out when this function is expanded.

*/

static ALWAYS_INLINE unsigned int do_swap(unsigned int key,

struct k_spinlock *lock,

int is_spinlock)

{

...

if (new_thread != old_thread) {

#ifdef CONFIG_TIMESLICING

z_reset_time_slice();

#endif

old_thread->swap_retval = -EAGAIN;

#ifdef CONFIG_SMP

_current_cpu->swap_ok = 0;

new_thread->base.cpu = arch_curr_cpu()->id;

if (!is_spinlock) {

z_smp_release_global_lock(new_thread);

}

#endif

sys_trace_thread_switched_out();

_current_cpu->current = new_thread;

wait_for_switch(new_thread);

arch_switch(new_thread->switch_handle,

&old_thread->switch_handle); //★コンテキストスイッチ★

}

...

前々回に紹介した新しいコンテキストスイッチの方式(arch_switch())を使っていることがわかります。

AArch64の新しい形式のコンテキストスイッチarch_switch() 実装、入り口

// zephyr/arch/arm/include/aarch64/arch_func.h

static inline void arch_switch(void *switch_to, void **switched_from)

{

z_arm64_call_svc(switch_to, switched_from); //★アセンブラ実装へ★

return;

}

// zephyr/arch/arm/core/aarch64/switch.S

GTEXT(z_arm64_call_svc)

SECTION_FUNC(TEXT, z_arm64_call_svc)

svc #_SVC_CALL_CONTEXT_SWITCH //★スーパーバイザーコール命令★

ret

アセンブラ側の実装では、いきなりスーパーバイザーコール命令(svc命令)をぶっ放して、スーパーバイザーコール例外を起こすだけになっています。AArch64は例外ハンドラ内でコンテキストスイッチを行う仕組みのようです。

arch_switch() の引数

関数arch_switch() はスレッドを2つ受け取ります。old_threadは切り替え元のスレッド、new_threadは切り替え先のスレッドです。old_thread -> new_threadにコンテキストスイッチするわけです。ただし直接スレッド構造体を受け取るわけではなく、若干クセのある渡し方をします。

第1引数new_thread->switch_handle(void * 型)は切り替え先のスレッド構造体へのポインタ(struct k_thread * 型)new_threadが入っています。このポインタをキャストするとnew_threadが求められます。

実はここには罠があり、何も実装せずにいるとnew_thread->switch_handleにはNULLが入ります。すると、あとでCONFIG_SMPを有効にした段階でwait_for_switch() 関数にてハングアップします。こんなのパッと見ではわかりません……。

switch_handleの初期化

// zephyr/kernel/include/kswap.h

/* New style context switching. arch_switch() is a lower level

* primitive that doesn't know about the scheduler or return value.

* Needed for SMP, where the scheduler requires spinlocking that we

* don't want to have to do in per-architecture assembly.

*

* Note that is_spinlock is a compile-time construct which will be

* optimized out when this function is expanded.

*/

static ALWAYS_INLINE unsigned int do_swap(unsigned int key,

struct k_spinlock *lock,

int is_spinlock)

{

...

if (new_thread != old_thread) {

...

sys_trace_thread_switched_out();

_current_cpu->current = new_thread;

wait_for_switch(new_thread); //★これ★

arch_switch(new_thread->switch_handle,

&old_thread->switch_handle);

}

if (is_spinlock) {

arch_irq_unlock(key);

} else {

irq_unlock(key);

}

return _current->swap_retval;

}

/* There is an unavoidable SMP race when threads swap -- their thread

* record is in the queue (and visible to other CPUs) before

* arch_switch() finishes saving state. We must spin for the switch

* handle before entering a new thread. See docs on arch_switch().

*

* Note: future SMP architectures may need a fence/barrier or cache

* invalidation here. Current ones don't, and sadly Zephyr doesn't

* have a framework for that yet.

*/

static inline void wait_for_switch(struct k_thread *thread)

{

#ifdef CONFIG_SMP

volatile void **shp = (void *)&thread->switch_handle;

while (*shp == NULL) { //★CONFIG_SMP有効でnew_thread->switch_handleがNULLだとこのループでハング★

k_busy_wait(1);

}

#endif

}

AArch64向けのスレッド作成する関数を良く見ると、しれっとswitch_handleを初期化しています。この処理はRISC-V向けには存在しないため、追加する必要がありそうです。

switch_handleの初期化

// zephyr/arch/arm/core/aarch64/thread.c

/*

* An initial context, to be "restored" by z_arm64_context_switch(), is put at

* the other end of the stack, and thus reusable by the stack when not needed

* anymore.

*/

void arch_new_thread(struct k_thread *thread, k_thread_stack_t *stack,

char *stack_ptr, k_thread_entry_t entry,

void *p1, void *p2, void *p3)

{

...

/*

* We are saving:

*

* - SP: to pop out entry and parameters when going through

* z_thread_entry_wrapper().

* - x30: to be used by ret in z_arm64_context_switch() when the new

* task is first scheduled.

*/

thread->callee_saved.sp = (uint64_t)pInitCtx;

thread->callee_saved.x30 = (uint64_t)z_thread_entry_wrapper;

thread->switch_handle = thread; //★ここで初期化している★

}

関数arch_switch() の第2引数 &old_thread->switch_handle(void ** 型)は切り替え元のスレッド構造体のswitch_handleのポインタです。switch_handleの値(たいていNULL)自体には意味がなくて、このポインタからold_threadが計算できることが大事です。

長くなってきたので続きは次回。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年9月29日

Zephyr OSで遊ぼう その13 - SMP対応の準備、コンテキストスイッチの実装、前編、ラッパー関数まで実装

目次: Zephyr

CONFIG_USE_SWITCHを有効にするとビルドエラーが発生しますので、都度対処します。

arch_thread_return_value_set()

最初はarch_thread_return_value_set() が二重定義だと怒られます。

arch_thread_return_value_set() が二重定義

../kernel/include/kernel_internal.h: At top level: ../kernel/include/kernel_internal.h:84:1: error: redefinition of 'arch_thread_return_value_set' arch_thread_return_value_set(struct k_thread *thread, unsigned int value) ^~~~~~~~~~~~~~~~~~~~~~~~~~~~

USE_SWITCHを有効にした場合、arch_thread_return_value_set() はカーネル側で定義されるので、アーキテクチャ側では実装不要です。

arch_thread_return_value_set() カーネル側の定義

// zephyr/arch/riscv/include/kernel_arch_func.h

static ALWAYS_INLINE void

arch_thread_return_value_set(struct k_thread *thread, unsigned int value)

{

thread->arch.swap_return_value = value;

}

// zephyr/include/arch/riscv/thread.h

struct _thread_arch {

uint32_t swap_return_value; /* Return value of z_swap() */

};

// zephyr/arch/riscv/core/offsets/offsets.c

GEN_OFFSET_SYM(_thread_arch_t, swap_return_value);

この辺りは要らないので #ifndef CONFIG_USE_SWITCHで囲って無効化します。

arch_switch

次はarch_switch() が未定義だと言われます。

arch_switch() が未定義

../kernel/include/kernel_arch_interface.h:126:20: warning: 'arch_switch' declared 'static' but never defined [-Wunused-function]

static inline void arch_switch(void *switch_to, void **switched_from);

^~~~~~~~~~~

この関数がUSE_SWITCHの本体です。他のアーキテクチャを見ると、arch_switch() はラッパー関数で、本体はアセンブラで書かれていることが多いようです。他の流儀に習っておきます。

arch_switch() ラッパー

// arch/riscv/include/kernel_arch_func.h

#ifdef CONFIG_USE_SWITCH

extern void z_riscv_switch(void *switch_to, void **switched_from);

static inline void arch_switch(void *switch_to, void **switched_from)

{

z_riscv_switch(switch_to, switched_from);

}

#else

...

肝心の中身はまた今度実装します。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年9月28日

Zephyr OSで遊ぼう その12 - SMP対応の準備、コンテキストスイッチのコンフィグ

目次: Zephyr

以前(2020年2月21日の日記参照)ご紹介したとおり、ZephyrのRISC-V向け実装はSMPに対応していません。Zephyrのマルチコア対応を有効にするコンフィグはCONFIG_SMPですが、有効にすると大量のエラーが出て、何から直したら良いのかわからなくなります。

コンフィグや実装を見た限りでは、下記の4つのステップで対応していくと良さそうです。

- (今ここ)SMPの前提条件、新しいコンテキストスイッチ方式に対応する(CONFIG_USE_SWITCH, CONFIG_USE_SWITCH_SUPPORTED)

- SMPに対応する(CONFIG_SMP)、ただしCPUコア数は1

- 先頭ではないコア(mhartid != 0)で動作させる、ただしCPUコア数は1

- CPUコア数を1以上にする(CONFIG_SMP)

このコンフィグを有効にすその前に対応すべきコンフィグがあります。CONFIG_USE_SWITCHとCONFIG_USE_SWITCH_SUPPORTEDです。

CONFIG_USE_SWITCH

// zephyr/kernel/Kconfig

config USE_SWITCH

bool "Use new-style _arch_switch instead of arch_swap"

depends on USE_SWITCH_SUPPORTED

...

config SMP

bool "Enable symmetric multithreading support"

depends on USE_SWITCH

既存の各アーキテクチャの対応状況を見ると、

CONFIG_USE_SWITCH対応状況(一例)

// ARM

// Aarch32はUSE_SWITCHは未サポート

// AArch64はCortex-AのみUSE_SWITCHをサポート

// zephyr/arch/arm/core/aarch64/Kconfig

config CPU_CORTEX_A

bool

select CPU_CORTEX

select HAS_FLASH_LOAD_OFFSET

select USE_SWITCH

select USE_SWITCH_SUPPORTED

// ARC

// ARCV2はUSE_SWITCHをサポート

// zephyr/arch/arc/Kconfig

config CPU_ARCV2

bool

select ARCH_HAS_STACK_PROTECTION if ARC_HAS_STACK_CHECKING || ARC_MPU

select ARCH_HAS_USERSPACE if ARC_MPU

select USE_SWITCH

select USE_SWITCH_SUPPORTED

default y

他は載せませんがAArch64, ARC, x86_64, xtensaが対応しているようです。

Zephyrのコンテキストスイッチ

Zephyrにはコンテキストスイッチが2種類存在しています。違いは下記の通りです。

- arch_swap: シングルコア専用のコンテキストスイッチ、RISC-Vは対応済み

- arch_switch: SMPに対応したコンテキストスイッチ、シングルコアだと若干効率が悪い、RISC-Vは未対応

CONFIG_USE_SWITCH_SUPPORTEDを有効にするにはarch_switchを実装する必要がありますが、RISC-Vではシングルコアもマルチコアもあり得ますから、CONFIG_USE_SWITCHを無条件に有効にするのは得策ではないと考えられます。

SoC側のKconfigで有効にしても良いですし、ユーザーにmenuconfigから選んでもらう手もあります。あまり悩んでも仕方ないので、ユーザーが選べるようにして先に進めます。RISC-VのKconfigにSMP対応かどうか?を選べるコンフィグを一つ追加します。

CONFIG_USE_SWITCHを有効にするRISC-V向けコンフィグを追加

// zephyr/arch/riscv/Kconfig

config RISCV_SMP

bool "Does SOC has SMP"

select USE_SWITCH

select USE_SWITCH_SUPPORTED

有効にするとビルドエラーだらけになります。続きはまた今度。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年9月22日

今Steamで3DMarkが安い

目次: ゲーム

Steamのセールで3DMarkが意味不明なほど安くなっていたので、買いました。Steamは突然90%OFFとか平然とやってくるので、定価とは……??という気分になります。

新しいマシンを買う(もしくはパーツを買う)時に役に立ちそうです。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年9月20日

ヘッドフォンが壊れた

以前(2012年11月8日の日記参照)買ったヘッドフォン(audio-technica ATH-TAD500)が壊れました。

イヤーパッドは無事ですが、ヘッドバンドの合皮部分が破れて、内部のプラスチックの芯が見えています。まさかイヤーパッドより先にヘッドバンドが壊れるとは思わなんだ。

8年もの長きにわたって頑張ってくれて本当にありがたかったです。とても良い製品でした。

ヘッドフォン探し

家や会社でいくつかヘッドフォンを使ってきてわかりましたが、長時間の使用において楽なのは圧倒的に「イヤーパッドが布地」のヘッドフォンです。合皮的な材質は汗で肌にくっついて嫌なのと、傷んでくるとバリバリ剥がれてきて不快です。

今使っているヘッドフォンの後継者としてはaudio-technica ATH-AD500X ですかね。上位グレードのATH-AD700X, ATH-AD900Xも布地のイヤーパッドで良さそうです。

しかし形が今使っているヘッドフォンとかなり似ているため、おそらく耳が痛くなる欠点も共通だろうと思われます。耳が痛いのは何とかしたいため、他社でも探すことにしました。

オーディオの世界は上を見るとキリがないですけど、10万とかするヘッドフォンは検討しません。違いが全くわからん。

新しいヘッドフォン

SENNHEISER HD 599を買いました。Amazonで22,000円くらいでした。以前購入(2020年8月1日の日記参照)したSONY MDR-HW700DSもそうでしたけど、購入に勇気が要るお値段です。

付け心地はとても軽く、耳も痛くなりません。耳が痛いのは辛かったので、非常にありがたいです。あと、色が良いですね。ヘッドフォンはたいてい真っ黒けですけど、HD 599は白と茶という面白い色です。

難点は長時間使っていると頭のてっぺんが痛くなることです。ヘッドバンドは柔らかいクッションが入っていますが、カーブが自分の頭の形と合わないようです。

耳の問題が解決したと思ったら、今度は頭が痛くなるとは……想定外でした。うーん。

音質

正直、音質は良いね!ってくらいしかわからんですが、ドスドスした低音や、キンキンした高音は目立たず、フラットな印象です。

キンキンした音は断然Superlux HD681B(2019年8月25日の日記参照)の方が強いですし、低音はaudio-technica ATH-TAD500の方がやや強いです。

鳴らないわけじゃなくて、目立たないバランスになっているだけなので、気に入らないならイコライザでいじれば好きなテイストにできます。能力は高いからカスタマイズ自由って感じですね。

コメント一覧

- hdkさん(2020/09/23 12:26)

うちのATH-AD300もやはり頭にプラスチックパーツが直に当たるようになりましたが、小一時間なら我慢できるのでそのまま使っています(^^; 布地のイヤーパッドは長持ちしていいですよね。 - すずきさん(2020/09/24 00:23)

ありゃー、同じ壊れ方ですね。

新たなヘッドフォンは買わないんですか? - hdkさん(2020/09/24 21:43)

最近は音楽聞く時やビデオ視聴時はミニコンポを使っているので、ヘッドフォンは仕事の電話会議にしか使っていないんですよね...

この記事にコメントする

この記事にコメントする

| < | 2020 | > | ||||

| << | < | 10 | > | >> | ||

| 日 | 月 | 火 | 水 | 木 | 金 | 土 |

| - | - | - | - | 1 | 2 | 3 |

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

最近のコメント5件

最近の記事20件

-

23年4月10日

23年4月10日

すずき (03/15 18:17)

「[Linux - まとめリンク] 目次: Linux関係の深いまとめリンク。目次: RISC-V目次: ROCK64/ROCK...」 -

25年3月7日

25年3月7日

すずき (03/15 18:16)

「[wchanとptrace_may_access()] 目次: Linux以前、LinuxのI/O統計情報が読めないプロセス(...」 -

25年3月3日

25年3月3日

すずき (03/15 00:32)

「[健康保険料率] 給与明細を見ていて、なんか健康保険料がやたら高くないか……?と気になりました。要...」 -

22年11月14日

22年11月14日

すずき (03/14 23:35)

「[電池 - まとめリンク] 目次: 電池ニッケル水素電池(Ni-MH)やリチウムイオン電池などの二次電池。ニッケル水素電池の使...」 -

25年3月14日

25年3月14日

すずき (03/14 23:34)

「[ナトリウムイオン電池] 目次: 電池エレコムからナトリウムイオン電池を使用したモバイルバッテリーが発売されていたので予約しま...」 -

25年3月11日

25年3月11日

すずき (03/12 21:15)

「[首都高バトルSteam版、大体クリア] 目次: ゲームやっと首都高バトル(Steam版)のWondererを全員倒し、ミスタ...」 -

21年12月28日

21年12月28日

すずき (03/12 21:14)

「[ゲーム - まとめリンク] 目次: ゲーム一覧が欲しくなったので作りました。Wizardry(囚われし亡霊の街)敵が強すぎる...」 -

25年3月1日

25年3月1日

すずき (03/12 00:21)

「[レガシィの半年点検(2025)] 目次: 車先週、ディーラーに半年点検に持っていったら毎度おなじみのバッテリーがイカレていて...」 -

23年5月15日

23年5月15日

すずき (03/12 00:18)

「[車 - まとめリンク] 目次: 車三菱FTOの話。群馬県へのドライブ1群馬県へのドライブ2将来車を買い替えるとしたら?FTO...」 -

25年3月10日

25年3月10日

すずき (03/12 00:06)

「[誕生日] 42歳になりました。昨年の日記(2024年3月10日の日記参照)を見ると、リモートワークの話をしていました。最近は...」 -

25年2月19日

25年2月19日

すずき (03/01 15:49)

「[LinuxのI/O統計情報が読めないプロセスの謎を追う] 目次: Linux前回はsystemd --userの/proc/...」 -

25年2月18日

25年2月18日

すずき (02/25 01:12)

「[LinuxのI/O統計情報が読めないプロセスが居る] 目次: LinuxLinuxのI/O統計情報(/proc/[pid]/...」 -

23年4月28日

23年4月28日

すずき (02/23 00:31)

「[Linuxの/dev/zeroの実装] 目次: LinuxTwitterで/dev/zeroの話をしている人が居て、そういえ...」 -

25年2月17日

25年2月17日

すずき (02/23 00:29)

「[LinuxのI/O統計情報] 目次: LinuxLinuxは各プロセスがどれくらいI/Oを行ったか記録していて、procファ...」 -

25年1月23日

25年1月23日

すずき (02/20 00:27)

「[首都高バトルSteam版] 目次: ゲーム首都高バトルSteam版を買いました。首都高バトルシリーズは2006年の「首都高バ...」 -

25年2月4日

25年2月4日

すずき (02/16 23:34)

「[次のWindows 11でE480が見捨てられそう] 今使っているノートPC(Lenovo ThinkPad E480)のC...」 -

25年1月30日

25年1月30日

すずき (02/16 22:10)

「[Thunderbirdの消せないツールバー] Thunderbird 115.0(Supernova, 2023/07/11...」 -

25年2月3日

25年2月3日

すずき (02/16 18:37)

「[不思議なChromeの広告] Google ChromeでYahoo!を見ているとたまにChromeの広告が表示されます。C...」 -

25年1月27日

25年1月27日

すずき (02/16 16:37)

「[Ansibleのencrypted variablesをdecryptする] Ansibleのencrypt_stringで...」 -

21年5月22日

21年5月22日

すずき (02/12 00:33)

「[ベンチマーク - まとめリンク] 目次: ベンチマーク一覧が欲しくなったので作りました。最速のyes不安定なyesyesの高...」

こんてんつ

wiki

wiki Linux JM

Linux JM Java API

Java API過去の日記

2002年

2002年 2003年

2003年 2004年

2004年 2005年

2005年 2006年

2006年 2007年

2007年 2008年

2008年 2009年

2009年 2010年

2010年 2011年

2011年 2012年

2012年 2013年

2013年 2014年

2014年 2015年

2015年 2016年

2016年 2017年

2017年 2018年

2018年 2019年

2019年 2020年

2020年 2021年

2021年 2022年

2022年 2023年

2023年 2024年

2024年 2025年

2025年 過去日記について

過去日記についてその他の情報

アクセス統計

アクセス統計 サーバ一覧

サーバ一覧 サイトの情報

サイトの情報合計:

本日: